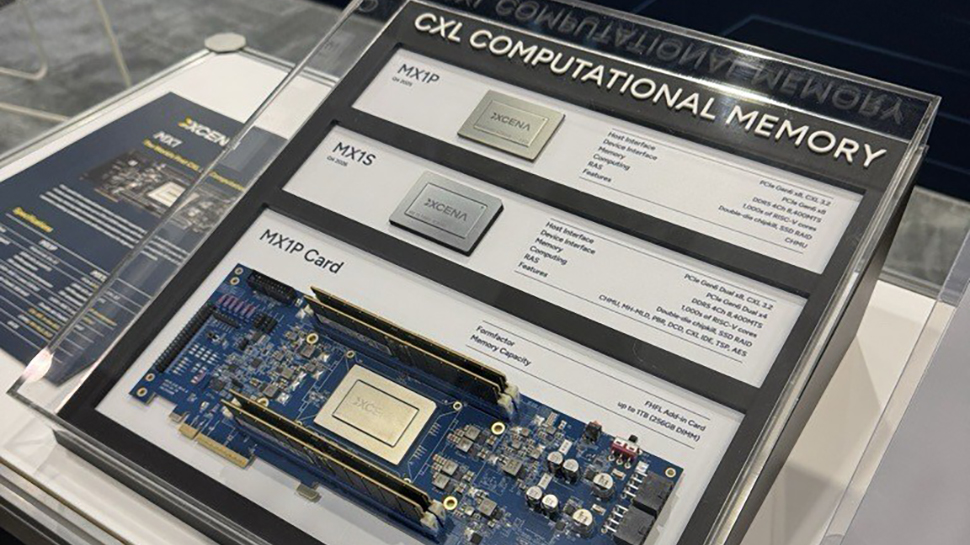

XCENA introduced MX1 computational memory with thousands of RISC-V cores at FMS 2025

techradar.com

At the recent FMS 2025 event (formerly Flash Memory Summit but now called Future of Memory and Storage to better suit its expanded focus), South Korean startup XCENA took the wraps off its first product, MX1 Computational Memory.

MX1 is built on the PCIe Gen6 and the Compute Express Link 3.2 standard. In putting compute directly next to DRAM, the chip is able to reduce the overhead of moving data back and forth between processors and memory.

Known as near-data processing, this approach could well influence how servers are designed in the years ahead.

Copyright of this story solely belongs to techradar.com . To see the full text click HERE